- Главная

- Компьютерные сети и технологии

- Микропроцессорные системы

- Цифровые устройства

- Оптоволоконные системы

Режимные зависимости динамических свойств транзистора

Рис. 41. Схема моделирования импульсных характеристик биполярного транзистора в схеме с общим эмиттером

Параметры моделирования:

.TRAN 0 9u 0 0.01u

.STEP V_V1 LIST 5 10 15 20

.PROBE V(alias(*)) I(alias(*)) W(alias(*)) D(alias(*)) NOISE(alias(*))

.INC " \SCHEMATIC1.net"

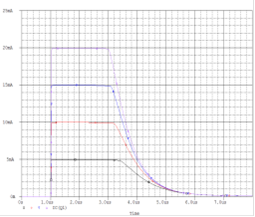

Рис. 42. Режимные зависимости импульсных свойств биполярного транзистора в схеме с общим эмиттером

Из графика видно, что время рассасывания уменьшается с увеличением напряжения на коллекторе, т.к. уменьшается толщина базы и в ней накапливается меньший заряд.

Читайте также

Проектирование радиовещательного приемника

Теория и техника радиоприемника быстро совершенствуется. Это требует от

специалистов постоянного изучения современной техники. Развитие радиоприемной

аппаратуры характеризуется в осн ...

Проектирование системы автоматического управления очистки стекла спортивного самолета

Задачи

по управлению тем или иным явлением или процессом, возникающие в повседневной

практической деятельности человека обширны и многообразны.

Управление

можно определить как совоку ...

Проектирование релейной защиты и автоматики

В электрической системе имеются следующие источники: ТЭЦ-1, ТЭЦ-2,

ТЭЦ-3, ТЭЦ-4, ТЭЦ-5, ГРЭС, СарГЭС и БАЭС. ТЭЦ-1, ГРЭС допускается отдельно не

учитывать, так как их мощность по сравнению с ...