- Главная

- Компьютерные сети и технологии

- Микропроцессорные системы

- Цифровые устройства

- Оптоволоконные системы

Структурная организация микроконтроллера MCS-51

Устройство портов

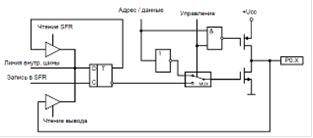

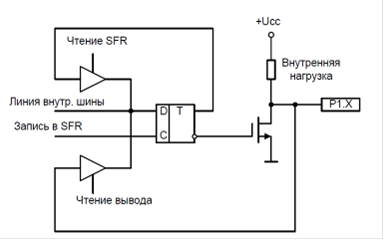

Каждый из портов содержит регистр-защелку (SFR P0 - SFR P3), выходную цепь и входной буфер.

Рисунок 5.1.6.1 - Порт P0

Рисунок 5.1.6.2 - Порт P1

На рисунке изображены функциональные схемы регистров-защелок и буферов ввода-вывода всех портов. Каждый из разрядов регистра-защелки SFR является D-триггером, информация в который заносится с внутренней шины данных микроконтроллера по сигналу «Запись в SFR Pх» (х= 0, 1, 2, 3) от центрального процессорного элемента (CPU). С прямого выхода D-триггера информация может быть выведена на внутреннюю шину по сигналу «Чтение SFR Pх» от CPU, а с вывода микросхемы («из внешнего мира») по сигналу «Чтение выводов Pх». Одни команды активизируют сигнал «Чтение SFR PI», другие - «Чтение выводов РI».

Особенности электрических характеристик портов

Выходные каскады триггеров SFR портов Р1 - РЗ выполнены на полевых транзисторах с внутренней нагрузкой, в то время как аналогичные каскады триггеров SFR P0-на транзисторах с открытым стоком. Каждая линия любого из портов может независимо использоваться как для ввода, так и для вывода информации (для линий портов P0 и Р2 это справедливо тогда, когда они не используются для обращения к внешней памяти).

Для перевода любой линии портов Р1 - РЗ в режим ввода информации необходимо в соответствующий разряд SFR занести 1. При этом выходной полевой транзистор отключается. Внутренний нагрузочный резистор как бы «подтягивает» потенциал вывода к напряжению питания, в то время как внешняя нагрузка может сделать его нулевым. Выходные каскады порта P0 имеют иную структуру. Нагрузочный полевой транзистор линии порта включен только тогда, когда порт выводит 1 при обращении к внешней памяти. В остальных случаях нагрузочный транзистор отключен. Таким образом, при работе в режиме обычного ввода-вывода информации (как, например, порт Р1) выходные каскады порт» P0 представляют собой ступени на транзисторах с открытым стоком. Запись 1 в соответствующий бит SFR отключает и второй транзистор, что приводит к тому, что вывод БИС оказывается под «плавающим» потенциалом. Это позволяет использовать линии порта P0 как выводы с высоко импедансным состоянием.

Поскольку выходные каскады портов P1 - P3 имеют внутреннюю нагрузку, при переводе в режим ввода информации они становятся источниками тока для микросхемы или транзистора, нагруженных на данный.

Последовательный порт микроконтроллера MCS-51

Через универсальный асинхронный приемопередатчик UART (Universal Asynchronous Receiver-Transmitter) осуществляются прием и передача информации, представленной последовательным кодом (младшими битами вперед), в полном дуплексном режиме обмена. В состав приемопередатчика, называемого часто последовательным портом, входят принимающий и передающий сдвигающие регистры, а также специальный буферный регистр (SBUF) приемопередатчика.

Кроме того, работой последовательного порта управляют два служебных регистра

· Регистр управления/статуса приемопередатчика SCON

· Бит SMOD регистра управления мощностью PCON

Запись байта в буфер приводит к автоматической переписи байта в сдвигающий регистр передатчика и инициирует начало передачи байта. Наличие буферного регистра приемника позволяет совмещать операцию чтения ранее принятого байта с приемом очередного. Но если к моменту окончания приема байта предыдущий не был считан из SBUF, то он будет потерян.

Последовательный порт MCS-51 может работать в четырех различных режимах.

· Режим 0. Информация и передается, и принимается через вывод входа приемника (RXi, TXi). Принимаются или передается 8 бит данных. Через вывод выхода передатчика (TXD) выдаются импульсы сдвига, которые сопровождают каждый бит. Частота передачи бита информации равна 1/12 частоты кварцевого резонатора

· Режим 1. В этом режиме передаются через вывод TXD или принимаются через RXD 10 бит информации: старт-бит (0), 8 бит данных и стоп-бит (1) при приеме информации в бит RB8 регистра управления/статуса приемопередатчика SCON заносятся стоп-бит. Скорость приема/передачи - величина переменная и задается таймером.

Читайте также

Проектирование системы управления вентильным преобразователем

Вентильные преобразователи широко применяются для преобразования энергии,

вырабатываемой и передаваемой в виде переменного напряжения промышленной

частоты 50Гц в электрическую энергию др ...

Программно-аппаратный комплекс, позволяющий проводить эксперименты по одновременному управлению несколькими мобильными объектами

В настоящее время в области искусственного интеллекта (ИИ) происходят

заметные преобразования. Источниками этих преобразований служат распределенный

искусственный интеллект (РИИ), центра ...

Особенности работы современного средства автоматической радиолокационной прокладки (САРП)

Устройство

компьютерной индикации, совмещенное со средствами автоматической

радиолокационной прокладки (САРП) и с электронной картографической системой,

размещаемых в ходовой рубке судн ...