- Главная

- Компьютерные сети и технологии

- Микропроцессорные системы

- Цифровые устройства

- Оптоволоконные системы

Архитектура ядра RISC

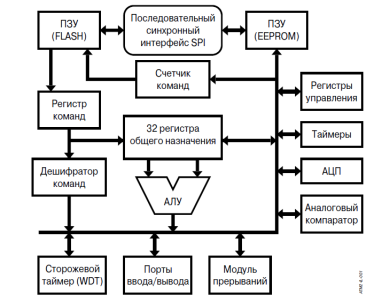

Ядро микроконтроллеров ATtiny семейства AVR выполнено по усовершенствованной RISC (enhanced RISC) архитектуре, в которой используется ряд решений, направленных на повышение быстродействия микроконтроллеров.

Арифметико-логическое устройство (АЛУ), выполняющее все вычисления, подключено непосредственно к 32-рабочим регистрам, объединенным в регистровый файл. Благодаря этому АЛУ выполняет одну операцию (чтение содержимого регистров, выполнение операции и запись результата обратно в регистровый файл) за один машинный цикл. Кроме того, в микроконтроллерах ATtiny семейства AVR каждая из команд занимает только одну ячейку памяти программ.

Такая организация позволяет одновременно работать как с памятью программ, так и с памятью данных. Разделение шин доступа позволяет использовать для каждого типа памяти шины различной разрядности, а также реализовать конвейеризацию. Конвейеризация заключается в том, что во время исполнения текущей команды производится выборка из памяти и дешифрация кода следующей команды.

В отличие от RISC-микроконтроллеров других фирм, в микроконтроллерах AVR используется 2-уровневый конвейер, а длительность машинного цикла составляет всего один период кварцевого резонатора. В результате, при более низкой тактовой частоте они могут обеспечивать ту же производительность, что и RISC-микроконтроллеры других фирм. [4, с. 30]

Архитектура ядра микроконтроллеров ATtiny семейства AVR показана на рис. 2.

Рисунок 2 - Архитектура ядра микроконтроллеров ATtiny семейства AVR

Читайте также

Проект участка сети доступа по технологии PON г. Новосибирска

Современное

общество - информационное общество. Жизнь и деятельность человека неразрывно

связана с информацией, ее хранением, передачей и обработкой, Объем данных

передаваемых по канала ...

Нанотехнологии в науке и технике

В течение тысячелетий человек использовал в быту и технике

макроскопические тела, состоящие из большого числа атомов, будь это каменный

топор или авиалайнер. Первая научно- ...

Передаточная функция разомкнутой системы

1. Определить

передаточную функцию разомкнутой системы рис.1, представить её в канонической

.форме. Построить её логарифмические частотные характеристики.

2. Оценить

показатели к ...