- Главная

- Компьютерные сети и технологии

- Микропроцессорные системы

- Цифровые устройства

- Оптоволоконные системы

Модуль процессора

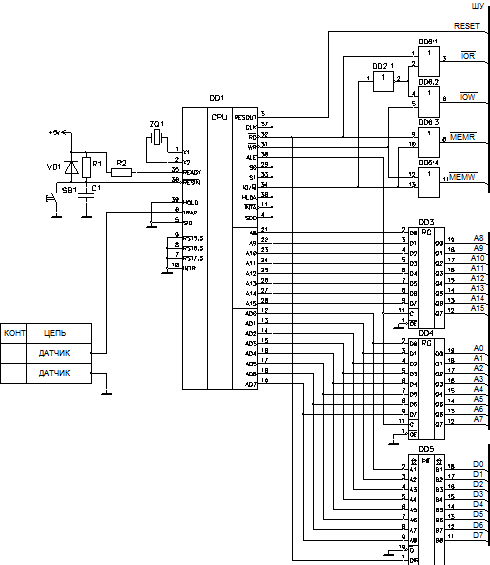

Модуль процессора изображён на Рис.

5.

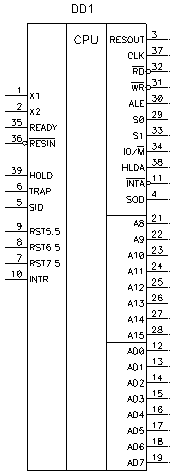

В качестве центрального процессора в данном курсовом проекте по условию задания будем использовать микропроцессор К1821ВМ85А (Рис. 4

), который является аналогом МП 80С85А фирмы INTEL.

Данный МП выполнен по КМОП-технологии, имеет одно напряжение питания +5 В, потребляет мощность 0,1 Вт. В данном МП имеется внутренний тактовый генератор, развитая система прерываний, МП имеет одинаковую систему команд с процессором КР580ВМ80. Также данный процессор имеет вход и выход для последовательного ввода и вывода информации. Все входы и выходы МП имеют ТТЛ уровни, нагрузочная способность - не более 1 ТТЛ нагрузки.

Отметим особенность данного МП - адресная информация МП пересылается в мультиплексном режиме. Старшие биты адресов считываются непосредственно с выводов микропроцессора, младшие - с шины данных во время выдачи МП сигнала ALE. Временное разделение с помощью строба ALE позволяет более эффективно использовать внешние выводы для организации работы с внешними устройствами.

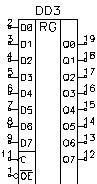

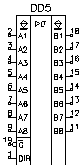

Шина управления формируется из управляющих сигналов микропроцессора с помощью логических элементов. Шины адреса и данных сформированы с расчётом на большее число входов, подключённых к этим шинам. Шина адреса формируется с помощью регистров КР1533ИР37 (DD3, DD4) (Рис. 2) с использованием сигнала фиксации адреса ALE. Шина данных формируется с помощью двунаправленного шинного формирователя КР1533АП26 (DD5) (Рис. 3) с использованием сигнала RD микропроцессора.

Рис. 2 Условно графическое обозначение К1533ИР37

Цоколёвка и назначение выводов микросхем приведены в приложении 1.

Рис. 3 Условно графическое изображение К1533АП6

Рассмотрим более подробно назначение выводов МП.

AD0-AD7 - двунаправленные выводы адрес\данные. По выдаче сигнала ALE передается младший байт адреса, в остальное время - байт данных.

A8-A15 - выводы старшего байта адреса

X1,X2 - выводы для присоединения времязадающей цепочки (кварцевого резонатора, RC или LC - цепочки)

RESOUT - сигнал сброса для внешних устройств

SOD,SID - выход и вход последовательных данных

TRAP - вход немаскируемого прерывания

RST7,5; RST6,5; RST5,5 - входы маскируемых прерываний

INTR - вход сигнала прерывания

![]() - сигнал подтверждения прерывания

- сигнал подтверждения прерывания

HOLD - вывод сигнала захвата шин внешними устройствами

HLDA - подтверждение получения сигнала захвата шин

CLC (OUT) - вывод сигнала тактовой частоты

![]() - сигнал внутреннего сброса

- сигнал внутреннего сброса

READY - вывод сигнала ожидания готовности внешних устройств

Рис. 4 Условно графическое изображение КР1821ВМ85А.

![]() - сигнал, показывающий, обращается МП к памяти или к портам ввода-вывода, S0,S1 - сигналы состояния устройства управления МП,

- сигнал, показывающий, обращается МП к памяти или к портам ввода-вывода, S0,S1 - сигналы состояния устройства управления МП, ![]() - сигнал чтения данных из ВУ,

- сигнал чтения данных из ВУ, ![]() - сигнал на запись данных во ВУ, ALE - сигнал фиксации младшего байта адреса

- сигнал на запись данных во ВУ, ALE - сигнал фиксации младшего байта адреса

Рис. 5 Модуль процессора.

Читайте также

Проект устройства со световыми эффектами на основе микроконтроллера ATtiny12 семейства AVR фирмы Atmel

Популярность микроконтроллеров ATtiny постоянно увеличивается.

Не последнюю роль в этом играет соотношение показателей «цена/ быстродействие/

энергопотребление», являющееся одним из ...

Разработка приемника УКВ-радиостанции

Радиоприемное

устройство - одно из важнейших и необходимых элементов радиотехнической системы

передачи сообщений. Оно обеспечивает: улавливание энергии электромагнитного

поля, нес ...

Оптоэлектронные технологии

Оптоэлектроника

- бурно развивающаяся область науки и техники. Многие ее достижения вошли в

быт: индикаторы, дисплеи, лазерные видеопроигрыватели. Разрабатывается

твердоте ...