- Главная

- Компьютерные сети и технологии

- Микропроцессорные системы

- Цифровые устройства

- Оптоволоконные системы

Построение сигнала телесигнализации

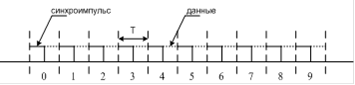

При передаче сигнала телесигнализации, в линию передается десять информационных импульсов, каждый из которых сопровождается синхроимпульсом (см. рисунок 6). Структура сигнала телесигнализации показана в таблице 5.

Рисунок 6 - Структура сигнала телесигнализации

Таблица 5 - Значение информационных битов сигнала телесигнализации

|

№ импульса |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

Значение |

старт |

№ тетрады |

состояние ключей |

стоп |

разрыв шлейфа | |||||

Рассмотрим работу платы ТС-32 при передаче первого стартового импульса сигнала телесигнализации. Для приема данных от платы ТС-32 плата сопряжения Ц-32 подает соответственно на «SYN+» положительный, а на «SYN-» отрицательный потенциал. Ток от SYN+ протекает через диод VD2, диод оптрона DA1, на SYN-. Открывается транзистор оптрона DA1 и на выводе RB5 (через вывод 7 общей шины) появляется уровень логического нуля «0». По этому значению процессор определяет, что пришел синхроимпульс и плата ТС-32 начинает передавать данные, а плата Ц-32 меняет потенциалы на SYN+ - отрицательный, SYN- - положительный. Для передачи информационного бита процессор платы ТС-32 выставляет на RB6 (вывод 6 общей шины) уровень логического нуля «0». При этом транзистор VT5 и соответственно диод оптрона DA1 остаются закрытыми и ток не протекает по цепи SYN-, транзистор оптрона DA1, диод VD4, SYN+. Выводы SYN+ и SYN- не закорачиваются, и плата Ц-32 принимает значение логического нуля «0», что соответствует стартовому импульсу.

Аналогично передаются и все остальные импульсы. Отличие будет только при передаче информационных импульсов. Для передачи логической единицы «1» процессор платы ТС-32 выставляет на выводе RB6 (вывод 6 общей шины) так же уровень логической единицы «1». Тогда ток протекает через транзистор VT5, диод оптрона DA1, резистор R2, на землю. Открывается соответствующий транзистор оптрона DA1 и ток протекает от SYN-, через транзистор оптрона DA1, диод VD4, на SYN+. Таким образом выводы SYN+ и SYN- оказываются закороченными и плата Ц-32 принимает значение логической единицы «1». Для передачи логического нуля «0» процессор платы ТС-32 понижает потенциал на выводе RB6 (вывод 6 общей шины) до уровня логического нуля «0». При этом транзистор VT5 и соответственно диод оптрона DA1 остаются закрытыми и ток не протекает по цепи SYN-, транзистор оптрона DA1, диод VD4, SYN+. Выводы SYN+ и SYN- не закорачиваются, и плата Ц-32 принимает значение логического нуля «0».

Таблица 6 - Назначение выводов процессора PIC16C57 платы ТС-32

|

Выводы |

Назначение Вывода |

|

RA0-RA3 |

Считывание состояния матрицы |

|

RC0-RC7 |

Управление вертикалями матрицы |

|

RB5 |

Прием синхроимпульсов для подготовки передачи данных |

|

RB6 |

Передача данных |

|

RB7 |

Управление индикацией |

Читайте также

Проектирование устройства для измерения статических характеристик электромагнитного двигателя

Ветер - это горизонтальное перемещение, поток воздуха параллельно земной

поверхности, возникающее в результате неравномерного распределения тепла и

атмосферного давления и направленное и ...

Моделирование мобильных систем связи

При организации сети сотовой связи для определения оптимального места

установки и числа базовых станций, а также для решения других задач необходимо

уметь рассчитывать характеристики сиг ...

Проект цифровой радиорелейной линии г. Волгоград – г. Астрахань

Связь всегда имела большое значение в жизни людей. Особенную

важность связь приобрела в последние годы, поскольку многие сферы деятельности

человека, например бизнес, напрямую зависят от ...