- Главная

- Компьютерные сети и технологии

- Микропроцессорные системы

- Цифровые устройства

- Оптоволоконные системы

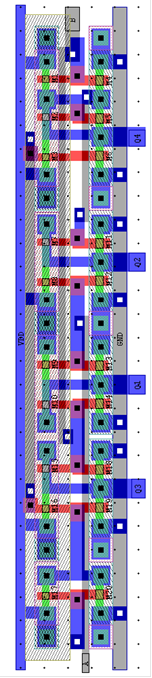

Топологический чертеж

Разработаем топологический чертеж заданной схемы в топологическом редакторе L-Edit САПР Tanner (рисунок 6).

Рисунок 6 - Топологический чертеж

Извлечем текстовое описание из топологии для проверки ее правильности. Получим:

* Circuit Extracted by Tanner Research's L-Edit Version 11.12 / Extract Version 11.12 ;

* TDB File: C:\sklf_tann\PC-OTK.tdb

* Cell: Cell0 Version 1.03

* Extract Definition File: \Program Files\Tanner EDA\L-Edit 11.1\samples\spr\example2\morbn20.ext

* Extract Date and Time: 06/26/2010 - 07:581 0 C=13.524fVDD 0 C=315.657fGND_3 0 C=260.654fGND_1 0 C=43.43fGND 0 C=43.43fGND_2 0 C=83.408f7 0 C=13.524f8 0 C=13.524fGND_4 0 C=43.43fB 0 C=62.99fA 0 C=56.996f12 0 C=13.524fVDD B GND_2 VDD PMOS L=3u W=3u AD=45p PD=30u AS=28.5p PS=19uGND_2 GND_2 1 VDD PMOS L=3u W=3u AD=28.5p PD=19u AS=21p PS=17u1 VDD VDD VDD PMOS L=3u W=3u AD=21p PD=17u AS=45p PS=30uGND_3 B GND_2 GND_3 NMOS L=4u W=3u AD=45p PD=30u AS=27p PS=18uGND_2 GND_2 GND_2 GND_3 NMOS L=4u W=3u AD=27p PD=18u AS=27p PS=18uGND_2 VDD GND_3 GND_3 NMOS L=4u W=3u AD=27p PD=18u AS=45p PS=30uGND_1 GND_2 8 VDD PMOS L=3u W=3u AD=45p PD=30u AS=21p PS=17u8 A VDD VDD PMOS L=3u W=3u AD=21p PD=17u AS=45p PS=30uVDD A 7 VDD PMOS L=3u W=3u AD=45p PD=30u AS=21p PS=17u7 B GND VDD PMOS L=3u W=3u AD=21p PD=17u AS=45p PS=30uGND_3 GND_2 GND_1 GND_3 NMOS L=4u W=3u AD=45p PD=30u AS=27p PS=18uGND_1 A GND_3 GND_3 NMOS L=4u W=3u AD=27p PD=18u AS=45p PS=30uGND_3 A GND GND_3 NMOS L=4u W=3u AD=45p PD=30u AS=27p PS=18uGND B GND_3 GND_3 NMOS L=4u W=3u AD=27p PD=18u AS=45p PS=30uGND_4 B 12 VDD PMOS L=3u W=3u AD=45p PD=30u AS=21p PS=17u12 VDD VDD VDD PMOS L=3u W=3u AD=21p PD=17u AS=45p PS=30uVDD A VDD VDD PMOS L=3u W=3u AD=48p PD=32u AS=45p PS=30uGND_3 B GND_4 GND_3 NMOS L=4u W=3u AD=45p PD=30u AS=27p PS=18uGND_4 VDD GND_3 GND_3 NMOS L=4u W=3u AD=27p PD=18u AS=45p PS=30uVDD A GND_3 GND_3 NMOS L=4u W=3u AD=45p PD=30u AS=45p PS=30u

* Total Nodes: 12

* Total Elements: 32

* Total Number of Shorted Elements not written to the SPICE file: 0

* Output Generation Elapsed Time: 0.000 sec

* Total Extract Elapsed Time: 14.781 sec

.END

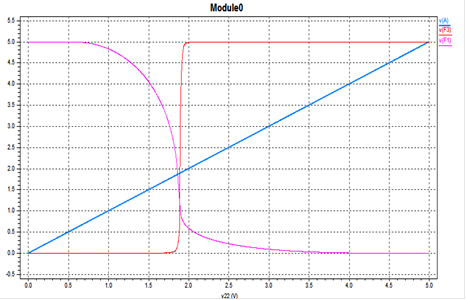

После проведения симуляции получаем передаточную характеристику (рисунок 7).

Рисунок 7 - Результаты моделирования извлеченного из топологии схемного описания

Из рисунка видно, что U0 = 0 , U1 = E = 4 В, UП = 1,85 В ≈ E / 2, значит топология построена правильно.

Заключение

В курсовом проекте произведен приближенный расчет электрических параметров КМОП-схемы «Искл-ИЛИ». На основе типового технологического процесса были рассчитаны электрофизические и конструктивные параметры компонентов схемы. Проведен схемотехнический анализ в программе T-Spice САПР Tanner. Разработан топологический чертеж, осуществлена его проверка с помощью извлечения текстового описания схемы и моделирования.

Читайте также

Проект внутризоновой ВОЛП на участке Новосибирск—Карасук

Научно-технический

прогресс во многом определяется скоростью передачи информации и ее объемом.

Возможность резкого увеличения объемов передаваемой информации наиболее полно

реализуется ...

Разработка комплекта электрических схем маршрутной релейной централизации блочного типа

Целью дипломного проектирование являлась разработка комплекта

электрических схем маршрутной релейной централизации блочного типа (БМРЦ) для

использования их студентами техникума в качест ...

Модуль дистанционного запуска двигателя автомобиля

Назначение устройства - производить запуск

двигателя с помощью SMS сообщения.

Курсовая работа состоит из 5 частей:

В первой части работы на основе технического

задания описывается ...