- Главная

- Компьютерные сети и технологии

- Микропроцессорные системы

- Цифровые устройства

- Оптоволоконные системы

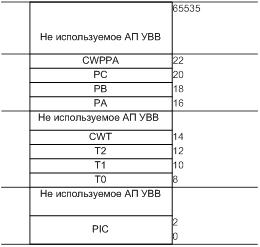

Карта распределения адресного пространства устройств ввода-вывода

В разрабатываемой МПС используется две микросхемы УВВ - ППА и ПИТ, в каждой из которых реализованы по четыре адресуемых устройства. Для микросхемы ППА это, соответственно, порты A, B и C (PA, PB и PC), а также регистр управляющего слова ППА (CWPPA). Для микросхемы ПИТ - это три таймера (T0, T1 и T2) и регистр управляющего слова ПИТ (CWPIT). В микросхеме ПКП адресуются 2 управляющих регистра.

Таким образом, из 65536 адресов адресного пространства ввода / вывода (АПУВВ), доступных МП, используется только 10.

Как и при распределении АПП, распределение адресов АПУВВ целесообразно произвести исходя из простоты реализации дешифратора АПУВВ. В связи с тем, что у процессора отсутствует адресная линия А0, нужно производить дешифрацию линий А4, А3, для адресации УВВ, а линиями А2, А1 адресовать внутренние регистры УВВ (рисунок 25).

Рисунок 25 - Распределение АПУВВ

Читайте также

Проектирование устройств фильтрации

Неотъемлемая часть телекоммуникационных задач связана с преобразованием

сигналов. Одной из основных является фильтрация, т.е. выделение или подавление

определенных частот сигнала. Устрой ...

Подвеска оптического кабеля на опорах

В

настоящее время на ВОЛП-ВЛ применяются следующие типы ОК:

ОКГТ

- оптический кабель, встроенный в грозозащитный трос;

ОКСН

- оптический кабель самонесущий;

ОКНН

- оптический ...

Проектирование системы автоматического управления очистки стекла спортивного самолета

Задачи

по управлению тем или иным явлением или процессом, возникающие в повседневной

практической деятельности человека обширны и многообразны.

Управление

можно определить как совоку ...